Het officiële persbericht

Enkele van de eerste afbeeldingen van een ontmantelde Intel Core Ultra 9 285K “Arrow Lake-S" processor zijn opgedoken op het web, wat een opgesplitst chiplet-gebaseerd processorontwerp bevestigt. Intel is overgestapt op chiplet-gebaseerde processors met zijn Core Ultra “Meteor Lake", waardoor het specifieke IP-blokken van de processor op verschillende foundry nodes kan bouwen, zodat degenen die de meest geavanceerde nodes niet nodig hebben, genoegen kunnen nemen met iets oudere nodes, waardoor Intels opbrengsten voor die geavanceerde node worden gemaximaliseerd. De foto van de matrijs toont een vergelijkbaar niveau van opsplitsing met “Meteor Lake" dan dat van de recentere Core Ultra 200V “Lunar Lake" mobiele processor.

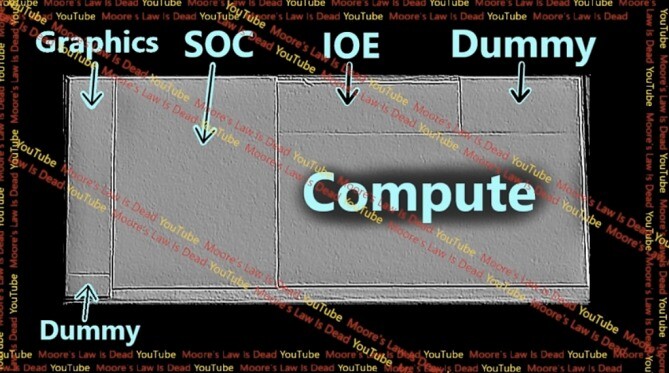

Met “Lunar Lake" heeft Intel een paar dingen opnieuw geaggregeerd. “Lunar Lake" heeft slechts twee tegels: een SoC-tegel en een I/O-tegel. De 3 nm SoC-tegel bevat het CPU-complex, een grote iGPU en een grote NPU van 40 TOPS-klasse, die allemaal die-ruimte delen met de geheugencontrollers en het PCIe root-complex. De kleinere 6 nm I/O tile bevat de PHY’s van de verschillende I/O interfaces. De “Arrow Lake" chip lijkt een vergelijkbare mate van opsplitsing te hebben als “Meteor Lake". We kunnen minstens vijf tiles zien die bovenop de Foveros basistegel zitten. De afbeelding heeft geen annotatie voor de verschillende tegels.

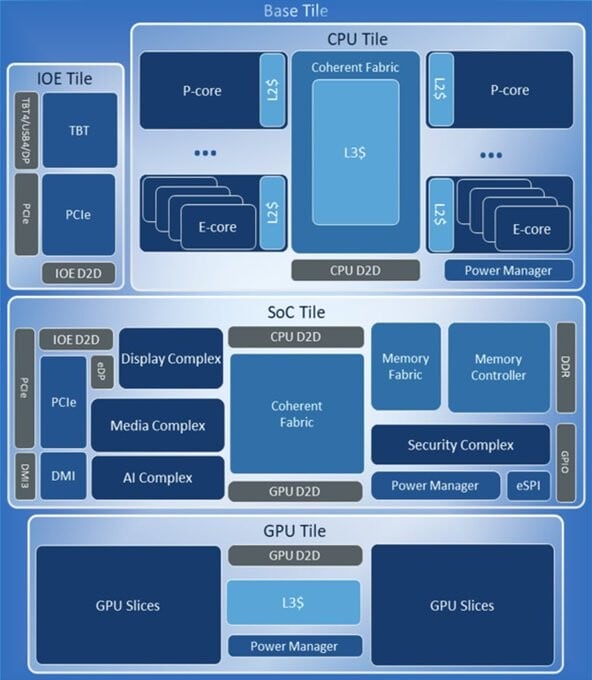

Het MLID-rapport zegt dat er een Compute-tegel zal zijn die de CPU-kernen bevat, een SoC-tegel, een Graphics-tegel, een breakout I/O-tegel en enkele dummy-tegels die zorgen voor structurele versterking, waardoor de chip een rechthoekige vorm krijgt. Het lek van Jay Kihn wijst erop dat de Compute tile de P-cores en E-core clusters bevat die in een conventionele ring-bus zijn gerangschikt en een L3 cache delen, vergelijkbaar met hoe het in de Compute tile van “Meteor Lake" is. Deze tegel bevat acht “Lion Cove" P-cores, elk met 3 MB eigen L2-cache (we weten dit van de Lunar Lake technische deep-dive), en vier “Skymont" E-core clusters, elk met 4 MB gedeelde L2-cache. Alle CPU cores delen een 36 MB L3 cache.

De Compute tile praat met de SoC tile, die de DDR5 geheugencontrollers, het PCIe Gen 5 root-complex, de beveiligingsprocessor, de display controller en de media acceleration engine bevat. Er is ook een “AI-complex", wat heel goed een NPU zou kunnen zijn. Het valt nog te bezien of dit de grotere NPU 4 is van Lunar Lake, die voldoet aan de Microsoft Copilot+ vereisten. De SoC-tegel levert wat I/O, zoals het DDR5-geheugen en een deel van de PCIe, maar vertrouwt op een breakout I/O-tegel voor meer PCIe-connectiviteit en geïntegreerde Thunderbolt.

Tot slot is er de Graphics tile, die de iGPU bevat, voornamelijk de Xe cores en alle hardware die de iGPU nodig heeft in de grafische rendering pipeline, inclusief een eigen L3 cache. De display controllers en mediaversnellers bevinden zich in de SoC tile en de display I/O bevindt zich in de breakout I/O tile. Als we kijken naar de grootte van de Graphics-tegel, dan zien we dat de desktopversie van “Arrow Lake" waarschijnlijk geen erg grote iGPU zal hebben, misschien maar maximaal twee Xe-kernen. Lunar Lake" heeft daarentegen een grote iGPU met 8 Xe cores, omdat het idee achter Lunar Lake dunne en lichte notebooks zijn zonder discrete graphics.

Bronnen: TechPowerUp, CodeCommando (Twitter), Moore’s Law is Dead (YouTube), Jay Kihn (Twitter), VideoCardz